The past three days (April 10–12, 2026) have finally brought the “Holy Grail” of spec confirmations for the Intel Z990 chipset and the LGA 1954 socket. Following a series of technical briefings for board partners, we have verified that the Z990 platform effectively ends the era of “bandwidth anxiety” by fundamentally decoupling GPU performance from high-speed storage.

Z990 Platform: 36 PCIe 5.0 lanes vs only 20 before!

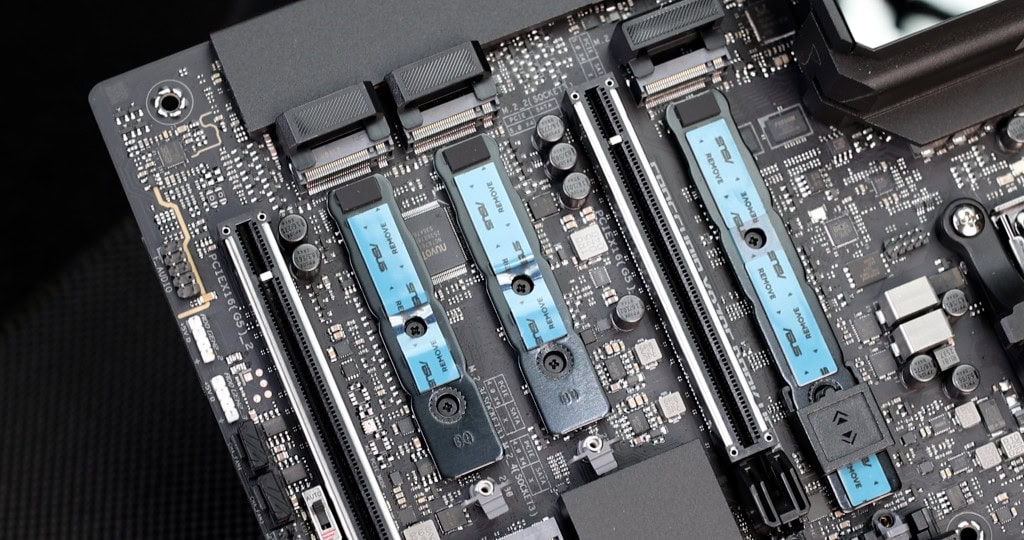

Confirmed as of April 10, 2026, the new and incoming line-up of Intel powered motherboard will effectively double the number of available PCIe 5.0 lanes, finally gapping and remedying to its late and disappointing PCIe 5.0 adoption seen on current Z890 powered motherboards.

| Component | PCIe 5.0 Lanes | PCIe 4.0 Lanes | Total Usable Lanes | Primary Usage |

| CPU (Nova Lake-S) | 24 | 0 | 24 | 16x for Graphics (GPU), 8x for high-speed M.2 NVMe storage. |

| PCH (Z990 Chipset) | 12 | 12 | 24 | Secondary M.2 drives, Thunderbolt/USB4, Networking (Wi-Fi/Ethernet), general I/O. |

| Platform Total | 36 | 12 | 48 |

Now we have 36 PCIe 5.0 lanes total !

BUT… these are not pooled lanes! Despite having enough PCIe 5.0 lanes ( in theory ), they cannot feed 2 GPU exports at full 16 lanes capacity each!

It is counterintuitive I know.

Only the CPU has the tracing and the bandwidth to feed 16 PCIe 5.0 lanes of a GPU export!( or 8 by 8 in a dual GPU setup ).

The ULTRA 400 class of Intel processors will have 24 PCIe 5.0 lanes, but strictly divided:

-

16 lanes to the GPU(s).

-

4 lanes to a first Gen 5 M.2 slot.

- 4 lanes to a second Gen 5 M.2 slot.

On the other hand, the Z990 chipset has 12 PCIe 5.0 lanes, but divided in 3 tracings of 4 lanes each:

-

4 lanes to a third Gen 5 M.2 slot.

-

4 lanes to a fourth Gen 5 M.2 slot.

-

4 lanes to a bottom PCIe x4 expansion slot.

After feeding the GPU export, the current Z890 powered boards struggle to keep a 2nd PCie 5.0 enabled NVMe. With the new Z990 platform, we can have upto FOUR PCIe 5.0 enabled NVMe fully fed ( 128 Gbs each ), in addition to a fully fed 16 PCie 5.0 lanes GPU export, and still have 4 lanes to spare for the secondary PCIe export.

That is a MASSIVE storage bump indeed. Just keep in mind that the PCH fed NVMes, will MIGHT face some DMI linked bottlenecking since it is limited to 4 PCIe 5.0 lanes.

The primary PCIe x16 slot is now electronically isolated for GPU use, receiving 16 dedicated PCIe 5.0 lanes from the CPU that cannot be “stolen” by M.2 slots. This is the most significant confirmation of the week: unlike previous generations where adding a Gen 5 SSD would force your GPU down to x8 mode, the Z990 architecture ensures your graphics card always has its own private, high-speed highway.

The LGA 1954 socket features a mandatory 2L-ILM (Dual-Lever) system to manage the increased physical length of Nova Lake-S processors. This confirmation, surfacing on April 11, validates concerns regarding CPU warping; the dual-lever design ensures even mounting pressure across the pin grid, which is essential for maintaining the integrity of the high-speed Gen 5 signal paths.

What about the other new Intel Chipsets you ask?

Intel PCHs confirmeds SPECS

| Feature | Z990 | W980 | Q970 | Z970 | B960 |

| Total Lanes | 48 | 48 | 44 | 34 | 34 |

| CPU USB4/TB4 Ports | 2 | 2 | 2 | 1 | 1 |

| DMI Gen5 Lanes | 4 | 4 | 4 | 2 | 2 |

| PCH PCIe 5.0 Lanes | 12 | 12 | 8 | 0 | 0 |

| PCH PCIe 4.0 Lanes | 12 | 12 | 12 | 14 | 14 |

| SATA 3.0 Lanes | 8 | 8 | 8 | 4 | 4 |

| USB 3.2 20G Ports | 5 | 5 | 4 | 2 | 2 |

| USB 3.2 10G Ports | 10 | 10 | 8 | 4 | 4 |

| USB 3.2 5G Ports | 10 | 10 | 10 | 6 | 6 |

| AI (CPU) OC | Yes | No | No | Yes | No |

| BCLK OC | Yes | No | No | No | No |

| Memory OC | Yes | Yes | No | Yes | Yes |

| ECC Support | No | Yes | No | No | No |

| Displays Supported | 4 | 4 | 4 | 4 | 4 |

Without surprise, the Z990 PCH (Chipset) has officially retired the PCIe 3.0 standard from its motherboards, moving to an equal mix of 24 PCIe 4.0 ( 2 GBs / lane ) and Pcie 5.0 ( 4 GBs / lane ) lanes configuration. This ensures that even “secondary” slots on the motherboard, typically used for capture cards or 10GbE networking, no longer suffer from legacy bottlenecks, provided the motherboard traces are built to spec.

DMI Gen 5 x4 is the new communication backbone connecting the CPU and the Z990 chipset, as confirmed in the latest technical manual leaks. While the lane count is narrower than the old x8 links, the move to Gen 5 doubles the effective bandwidth to 128 Gbps, giving the chipset more “breathing room” to handle the influx of native USB4 and WiFi 7 data.

Native USB4 (40Gbps) is now baked into the CPU, with specs confirming 8 reserved lanes specifically for high-speed external I/O. By dedicating these lanes at the CPU level, Intel ensures that plugging in a high-speed external drive or Thunderbolt dock won’t cause lag or drops in your internal storage or networking speeds.

More to come 🙂